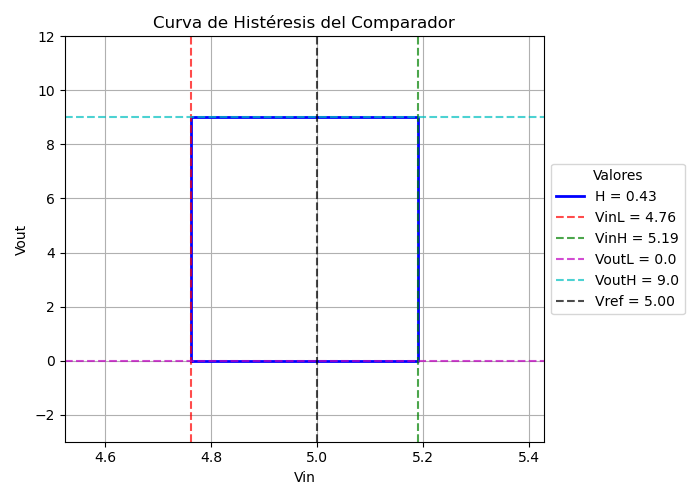

Diseño de PCB 6 capas para Sistema de Control Satelital Analógico

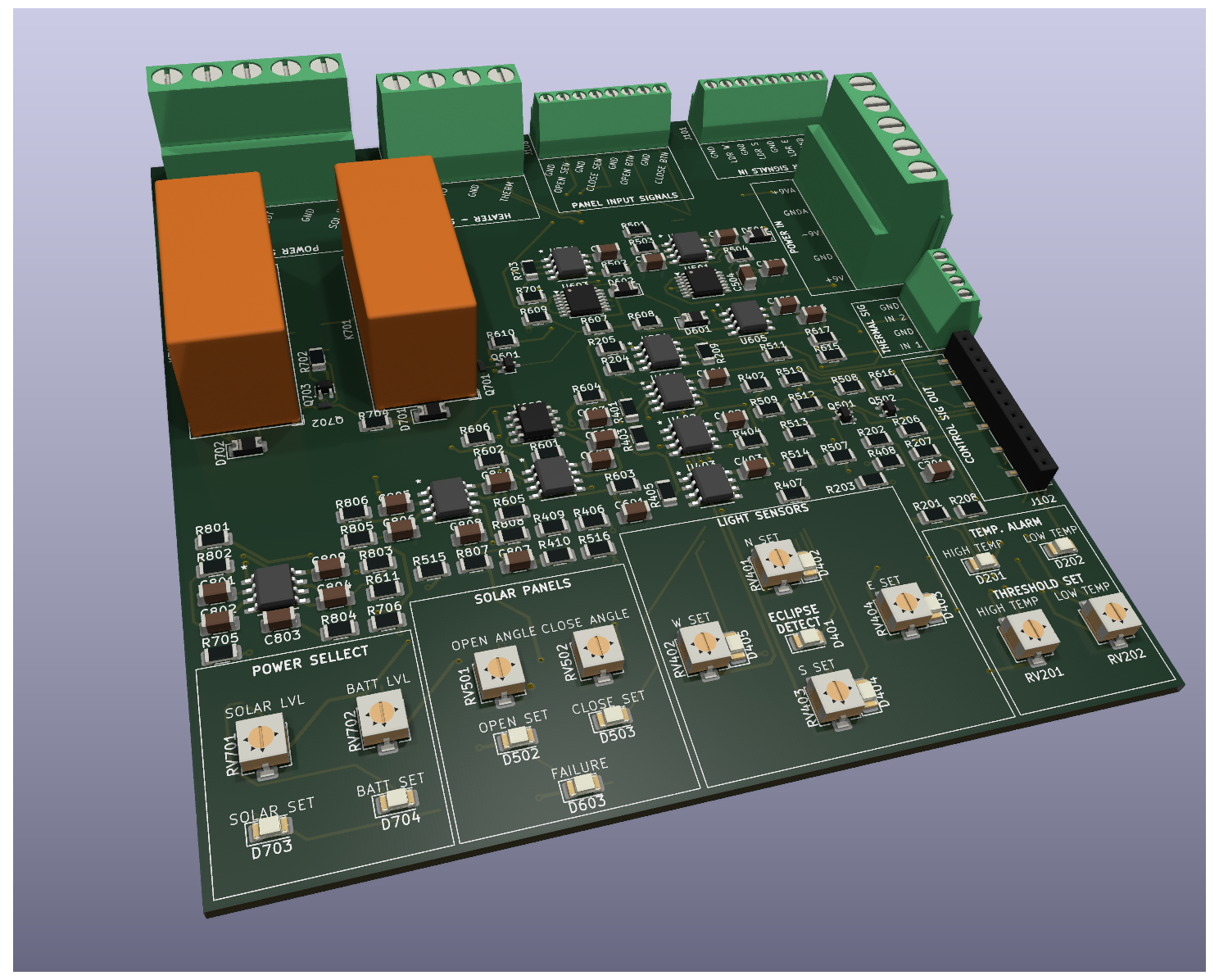

Render 3D del PCB principal - el cerebro analógico del sistema de control satelital

Repositorio del Proyecto:

https://github.com/SimonAulet/portfolio/tree/main/PCBContiene todos los archivos del proyecto: esquemáticos KiCad, diseños de PCB, simulaciones LTSpice, datasheets y librerías de componentes para importación directa.

Contexto

Desarrollo grupal de un sistema de control satelital analógico implementado con componentes discretos. El sistema integra detección de orientación mediante fotoresistencias, sensado térmico, generación de PWM analógica, posicionamiento de servomotor, circuitos de timing, latches analógicos y lógica de control autónoma.

Mi Contribución

Diseño integral en KiCad: Integración y desarrollo físico del sistema a partir de los módulos implementados en el laboratorio. Esto implica la creación del esquemático unificado en KiCad, selección estratégica de componentes compatibles con el montaje industrial, gestión de footprints y modelos 3D, implementación de clases de diseño para separación de señales (analógicas, digitales, potencia), routing crítico, y validación exhaustiva mediante ERC/DRC, culminando en un PCB de 6 capas listo para fabricación.

Simulación y validación analógica: Simulación en LTSpice de etapas clave: comparadores con histéresis (Schmitt trigger), generador de PWM analógico, circuitos de temporización, lógica de decisión para conmutación de fuentes vía relays, y latches implementados con transistores NPN.

Fase 1: La Arquitectura

Sistema general

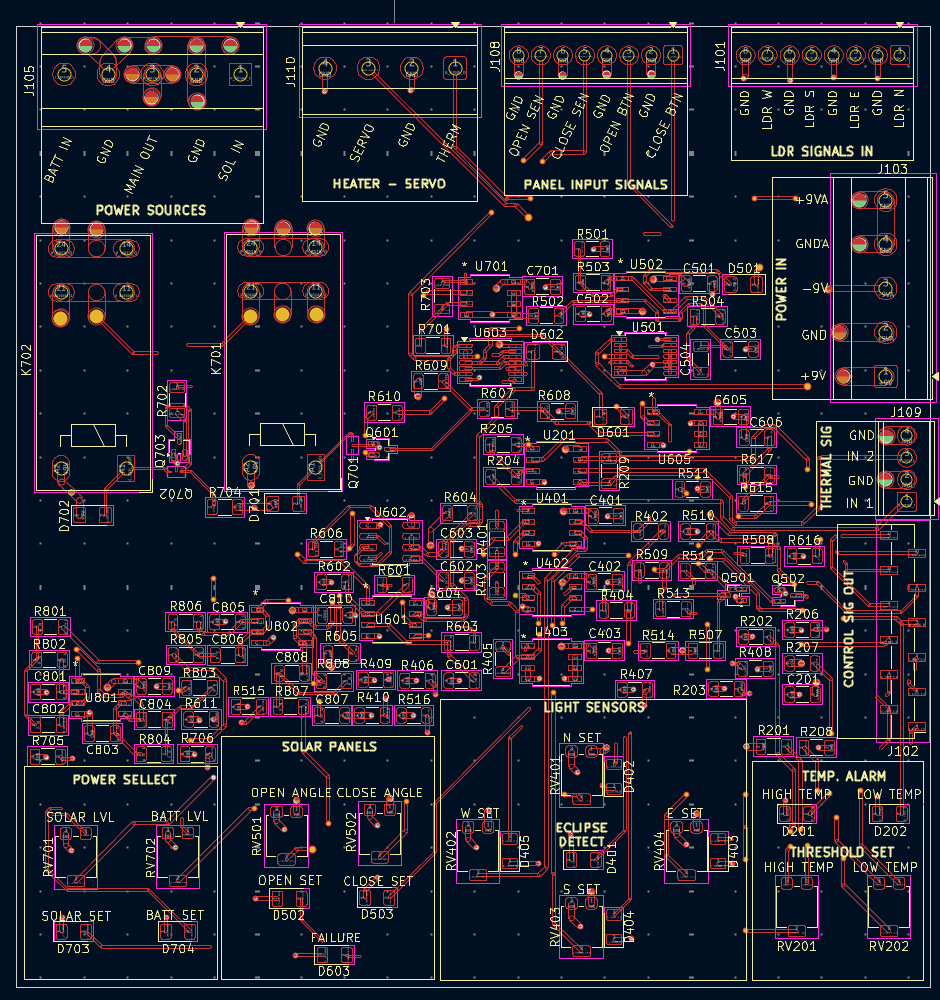

Hoja principal del esquemático - organizada como mapa de interconexiones entre subsistemas

El diseño se estructuró en 6 subsheets modulares, cada uno encapsulando una función específica:

- Filtrado activo para acondicionamiento de señales de sensores LDR

- Sensado de orientación para detección eclipse/posición

- Control térmico con sensado LM35 y actuación

- Despliegue de paneles solares con control PWM y verificación

- Verificación de despliegue mediante temporizadores 555

- Selector de fuente para conmutación automática entre solar/batería

La comunicación entre módulos se estableció mediante señales nombradas coherentemente usando prefijos. Por ejemplo A_ → Señales analógicas sensibles, C_ → Comandos y señales de control, F_ → Realimentación, L_ → Indicadores LED, etc. y sufijos para indicar entrada (_I) o salida (_O)

Planos Detallados

Esquemáticos completos del sistema con todos los componentes y conexiones detalladas.

Formato: PDF interactivo · Contenido: Esquemáticos completos

Descargar Esquemáticos (PDF)Selección de Componentes

Cada componente fue elegido considerando especificaciones eléctricas, disponibilidad, implicaciones de layout, y requerimientos térmicos/mecánicos. Se intentó usar todo del mismo fabricante (Texas Instruments) cuando fue posible:

| Componente | Fabricante | Características Clave | Razón de Selección |

|---|---|---|---|

| LM35 | Texas Instruments | Sensor de temperatura, TO-220 | Permite atornillado directo a baterías/fuentes de calor para medición precisa |

| LM358B | Texas Instruments | Op-amp dual, SMD, 0.1µF en Vcc | Estabilidad demostrada, compensación integrada, paquete compacto |

| CSD17577Q5A | Texas Instruments | MOSFET N-ch, 25V, 6.7mΩ | Eficiencia en conmutación, baja Rds(on), optimo para relés |

| RT314009 | TE Connectivity | Relay 9V/16A, 1 Forma C | Capacidad de corriente para conmutación de baterías, bobina compatible con 9V |

Consideraciones de layout: Los encapsulados SMD se priorizaron para reducir inductancias parásitas, mientras que componentes como el LM35 en TO-220 ubicados en sensores externos permitieron montaje mecánico robusto donde se requería transferencia térmica directa.

Fase 2: Implementación Física - PCB de 6 Capas

Estrategia de Stackup

La distribución en 6 capas se optimizó para garantizar integridad de señal y facilitar el debugging, con una separación clara de funciones:

| Capa | Designación | Contenido Principal | Consideración Clave |

|---|---|---|---|

| 1 | F.Cu (Top) | Señales analógicas críticas | Accesible para medición, trazos cortos |

| 2 | In1.Cu | Plano de tierra contínuo | Referencia de baja impedancia |

| 3 | In2.Cu | Distribución de alimentación | Separación entre potencia limpia y general |

| 4 | In3.Cu | Señales de control y setpoints | Aislamiento de rutas analógicas |

| 5 | In4.Cu | Interconexiones y LEDs | Capa utilitaria |

| 6 | B.Cu (Bottom) | Rutas analógicas de largo recorrido | "Autopistas" con routing predecible |

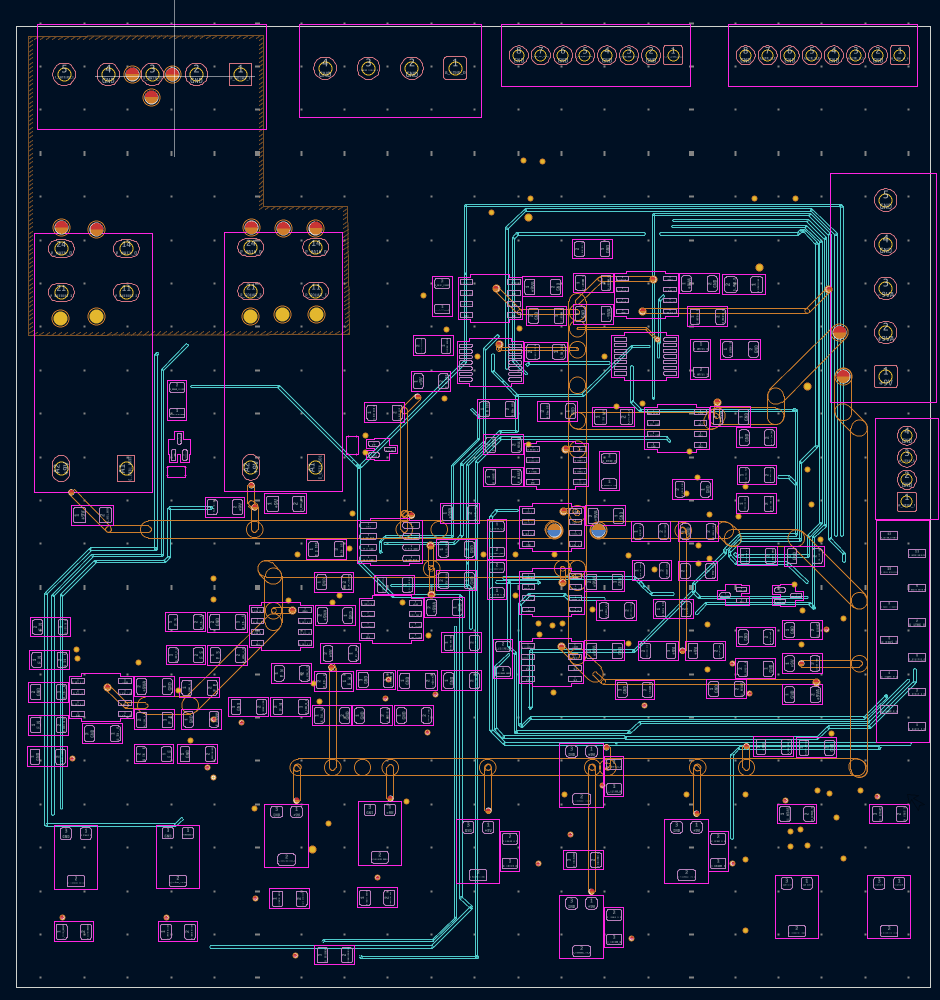

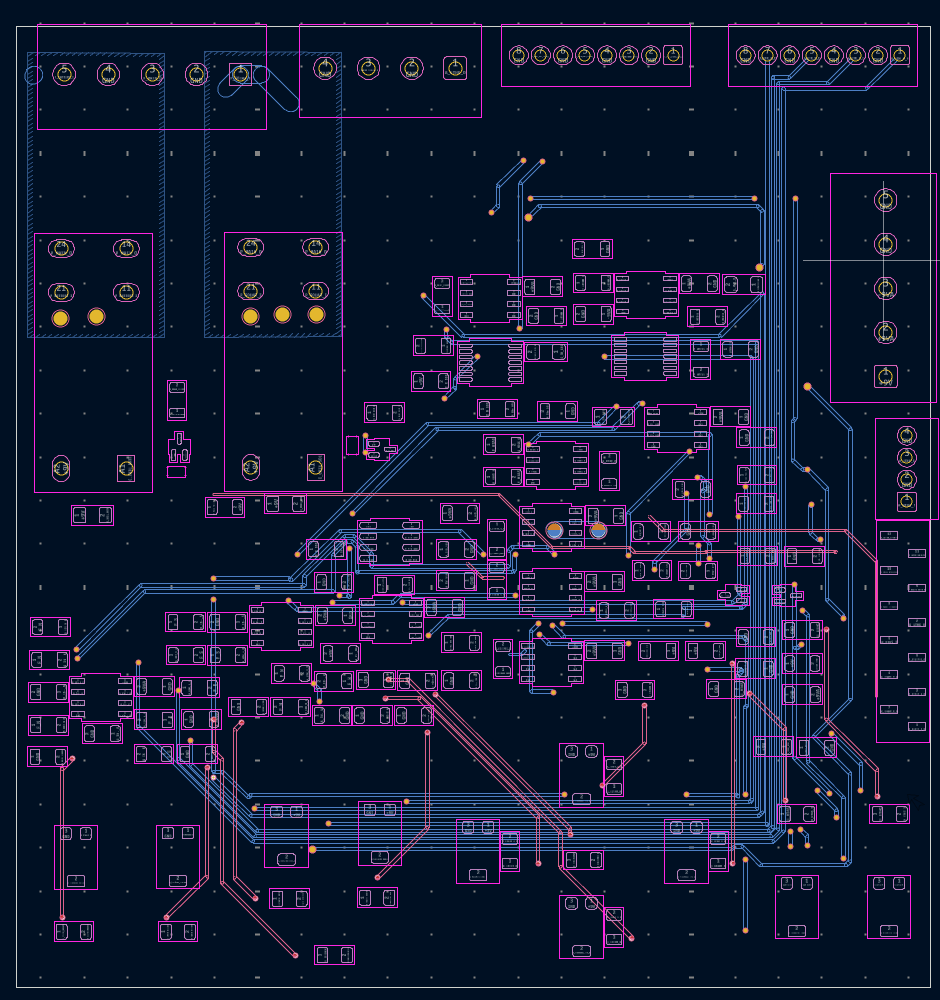

Visualización de Capas

F.Cu + In1.Cu

In2.Cu + In3.Cu

In4.Cu + B.Cu

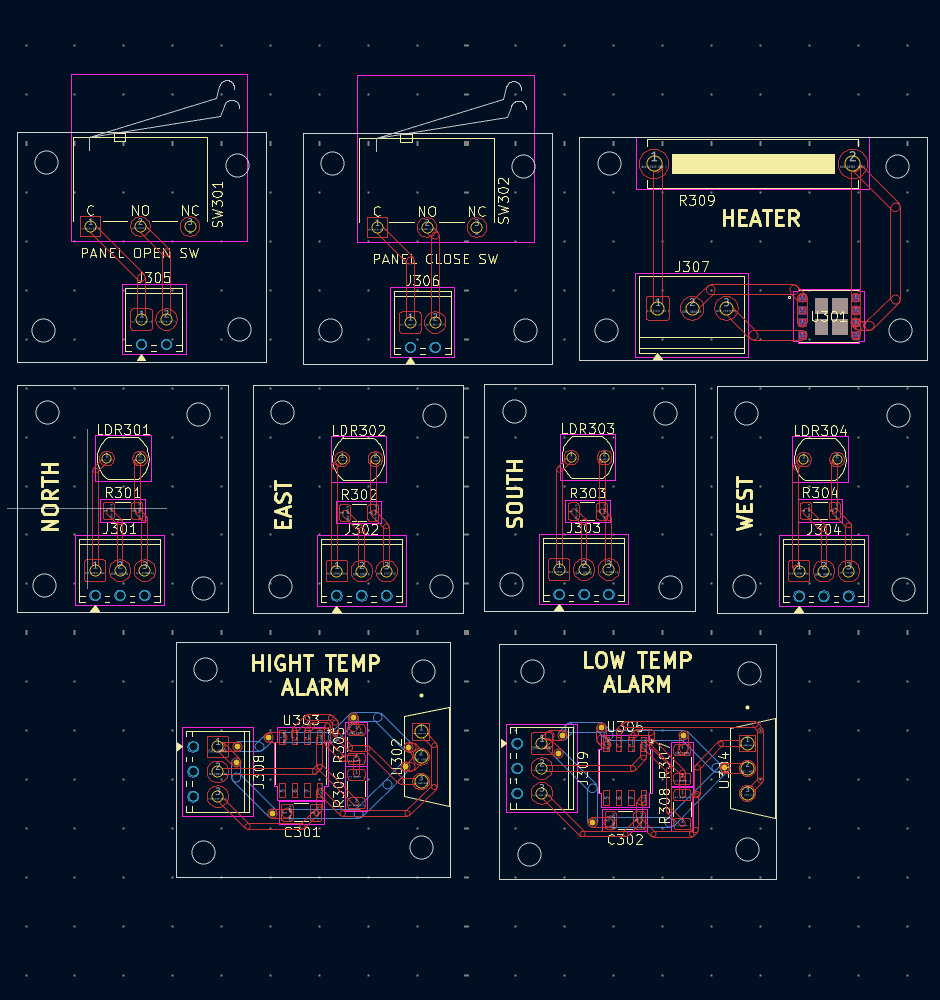

Módulos Sensoriales

Metodología de Routing

El routing siguió una jerarquía estricta, priorizando integridad sobre conveniencia:

- Tierra - Establecimiento de referencia con múltiples vías

- Alimentación - Trazos dimensionados según corriente requerida. Se separa alimentación de integrados (

power_clean) de alimentación general - Señales de feedback - Rutas directas y protegidas

- Señales analógicas - Minimización de longitud y cruces

- Control y LEDs - Completado de interconexiones

Esta secuencia aseguró que las señales más sensibles tuvieran rutas óptimas antes de comprometer espacio con funcionalidades secundarias.

Subsistemas Externos y Conectividad

Sensores y actuadores distribuidos - solución modular con conectividad claramente identificada

El sistema completo se extiende más allá del PCB principal mediante módulos externos:

- 4 módulos de detección de luz, cada uno con 1 LDR para cobertura omnidireccional.

- 2 sensores de temperatura LM35 para monitoreo térmico en ubicaciones críticas.

- 1 módulo heater activado por la señal de alerta de baja temperatura.

- 2 finales de carrera para detección física de apertura y cierre de paneles solares.

Cada módulo es un PCB cuadrado de doble capa con orificios para montaje mecánico robusto. La interconexión con el board principal se realiza mediante cables conectados a borneras rotuladas en ambos extremos, asegurando una instalación libre de errores y facilitando el mantenimiento o reemplazo individual de cualquier subsistema sin afectar al conjunto.

Puntos Clave del Diseño

- Separación efectiva de dominios: Las 63 señales organizadas en clases permitieron aplicar reglas de diseño consistentes y automatizadas.

- Routing jerárquico exitoso: Comenzar con referencia y alimentación, luego señales críticas, finalmente funcionalidades secundarias.

- Debugging incorporado: Todas las señales críticas accesibles en capas externas, con espacio para puntos de prueba donde fue necesario.

- Cumplimiento sobrado de especificaciones: El diseño final excede los requerimientos mínimos de clearance y ancho de trazo del fabricante seleccionado.

Simulación y Validación Analítica

Cada subsistema crítico del diseño se modeló y validó en LTSpice antes de cualquier implementación física. Partiendo de los requisitos funcionales —comparadores con histéresis, latches analógicos, temporizadores y generadores de PWM— se construyeron modelos utilizando componentes reales, como el opamp LM358 configurado según su datasheet de Texas Instruments, y señales PWL para simular condiciones operativas.

Este proceso de simulación permitió optimizar valores de componentes, verificar márgenes de diseño y predecir el comportamiento del sistema con alta precisión. Los resultados luego se correlacionaron exitosamente con mediciones en protoboard utilizando un osciloscopio Tektronix de gama alta, estableciendo una base sólida para el diseño final del PCB.

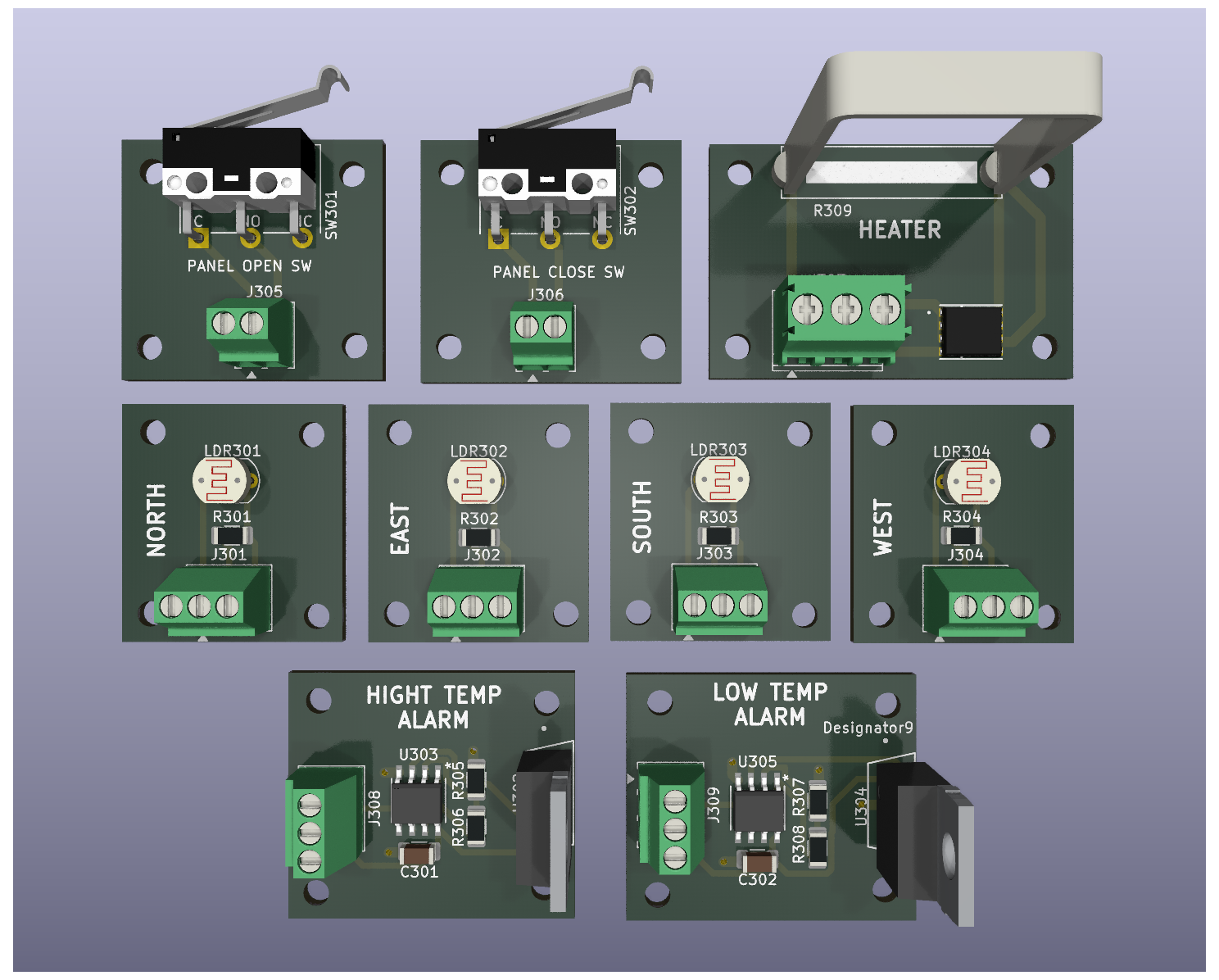

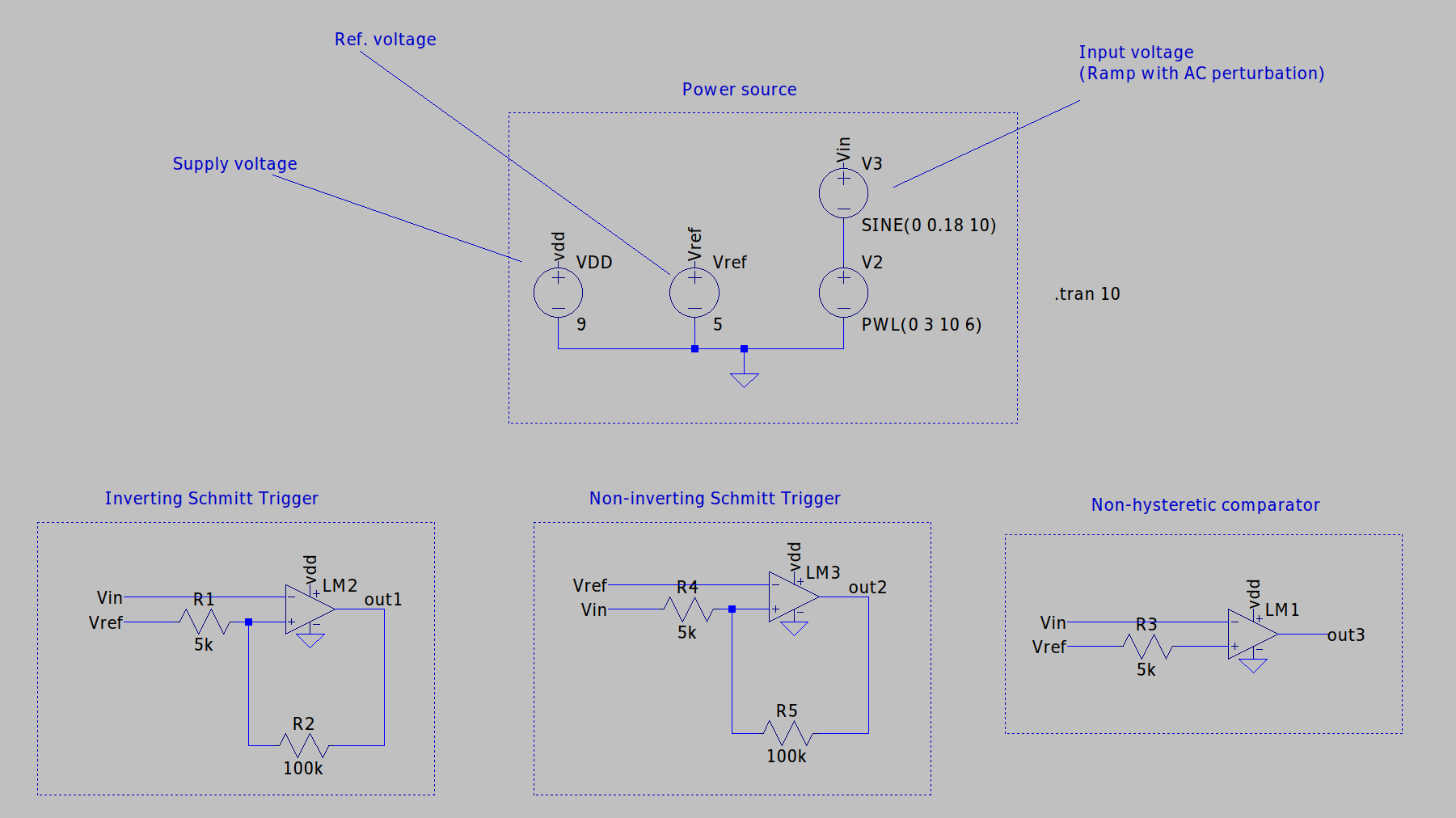

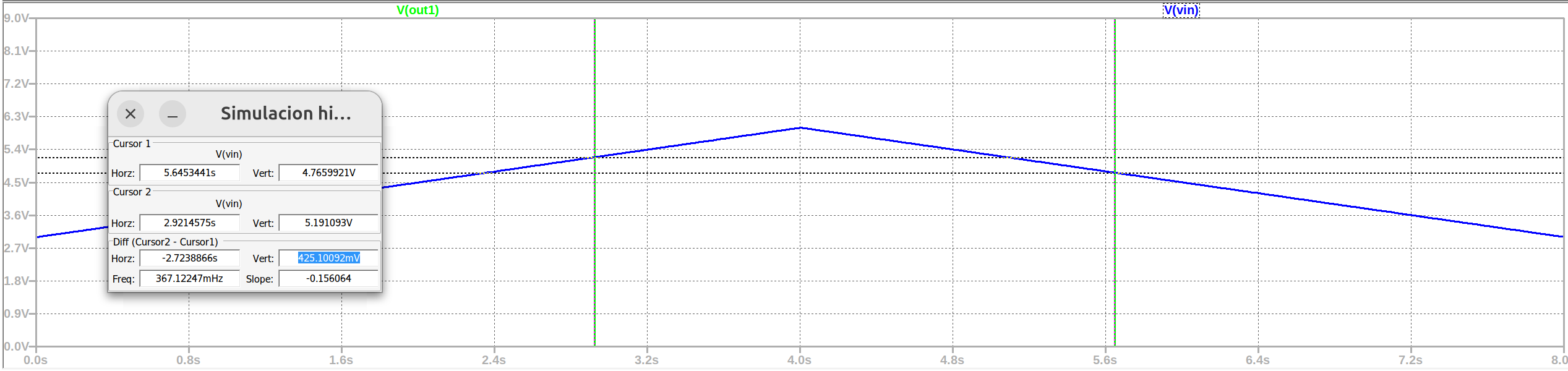

1. Comparador con Histéresis (Schmitt Trigger)

La histéresis se implementó para eliminar oscilaciones en la conmutación ante señales con ruido o variaciones lentas. El circuito se modeló en LTSpice y se caracterizó tanto analítica como experimentalmente.

Circuito implementado en LTSpice

Cálculo analítico: H = 0.43 V

Validación en simulación: ΔV = 425 mV entre umbrales

La simulación con una rampa triangular confirma que la conmutación ocurre con una diferencia de 425 mV entre los flancos de subida y bajada, en excelente acuerdo con el cálculo teórico de 430 mV. Esto asegura inmunidad a ruido y estabilidad en la detección de umbrales.

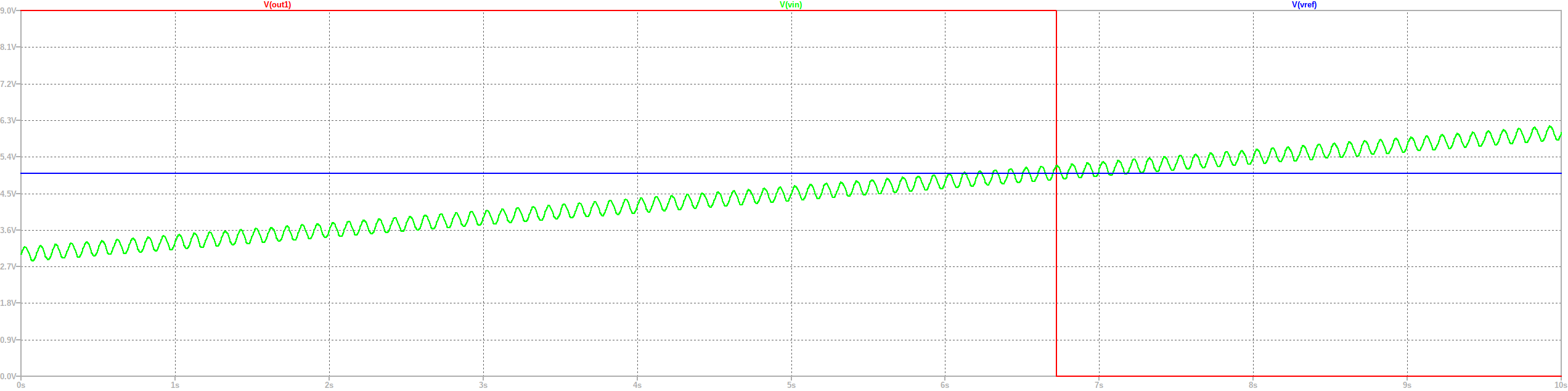

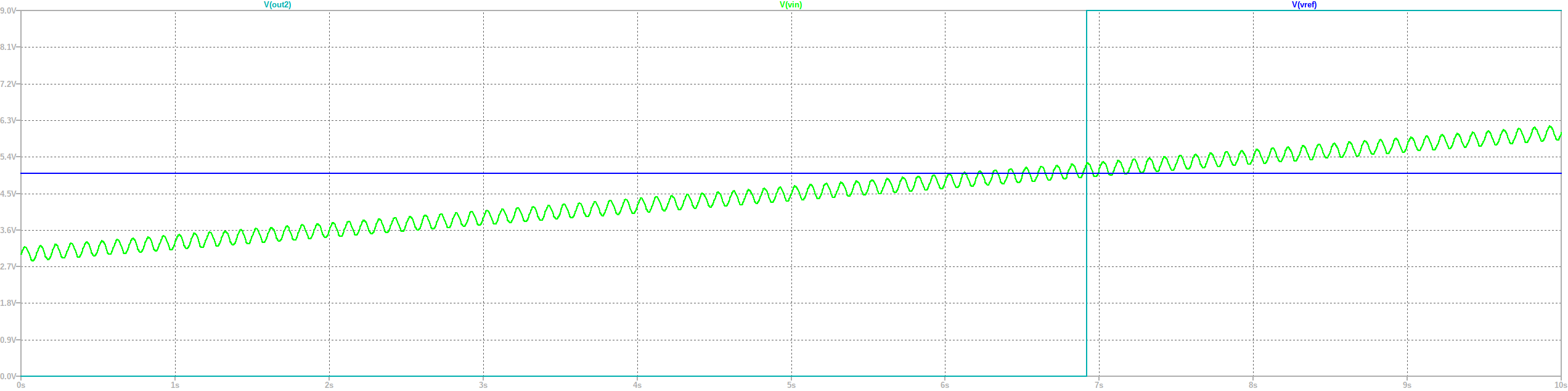

Configuración inversora con ruido

Configuración no inversora

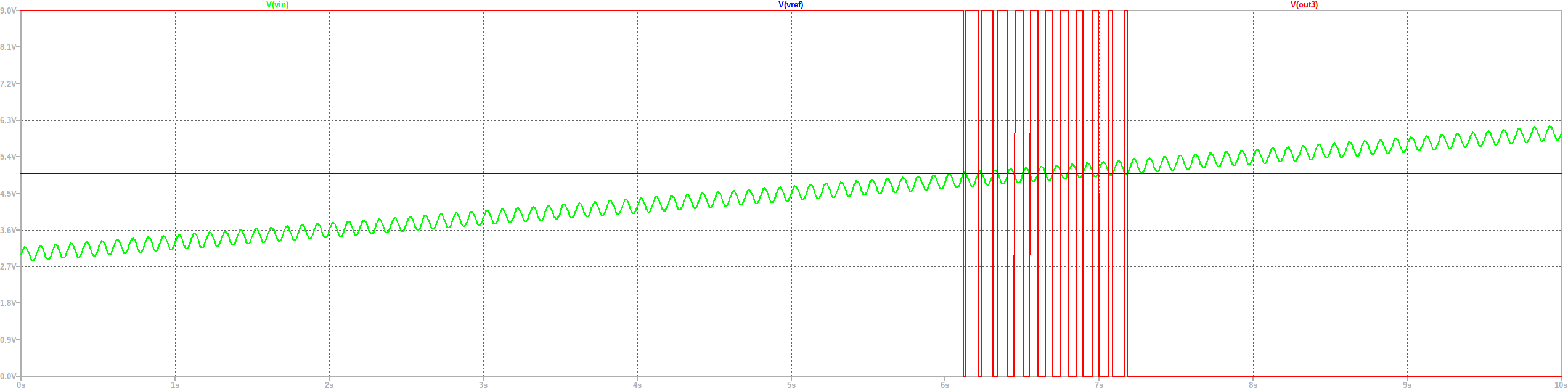

Sin histéresis: oscilaciones en el umbral

Las waveforms demuestran la efectividad del diseño: mientras el comparador sin histéresis presenta múltiples conmutaciones indeseadas al cruzar el umbral, ambas configuraciones con Schmitt trigger mantienen una salida limpia y estable incluso con señal de entrada ruidosa.

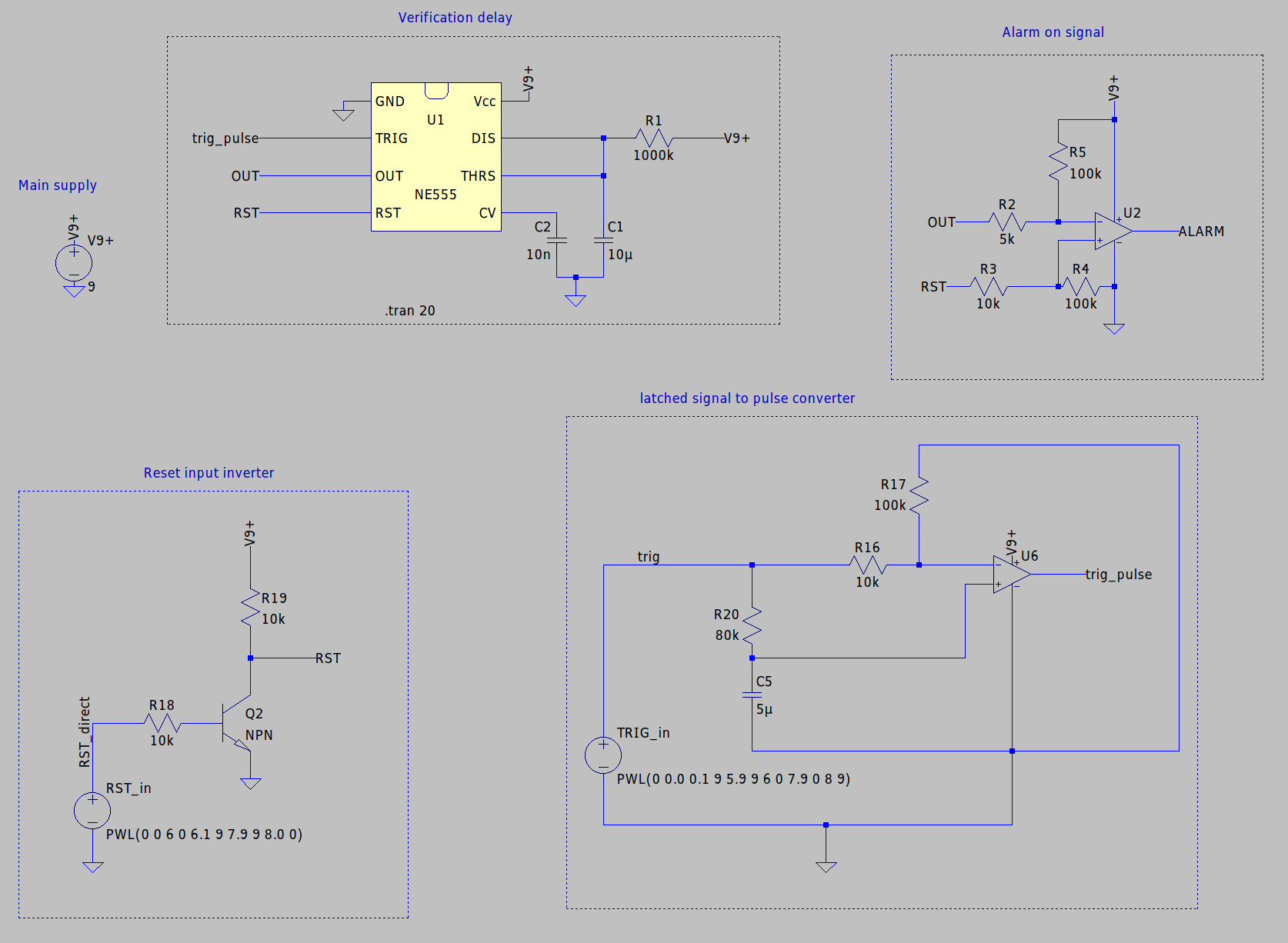

2. Temporización Analógica y Lógica de Alarma

El subsistema de temporización integra un temporizador 555, un circuito anti-latch personalizado y lógica de habilitación de alarma para garantizar que las señales de error se activen solo en condiciones válidas.

Circuito completo: temporizador 555, lógica de alarma y conversor latch-a-pulso

Conversor Latch-a-Pulso

Diseño original que resuelve un requerimiento específico: el 555 necesita un flanco, no una señal sostenida. Implementado con un LM358 y capacitor de 5 µF, genera un pulso corto en cada flanco de subida de la entrada, ignorando su estado posterior. Se utiliza dos veces en el sistema (para verificación de apertura y cierre de paneles).

.png)

Conversor latch-a-pulso anotado - convierte señal continua en pulso de activación

Comportamiento del Temporizador 555

El 555 opera con salida activa baja. La simulación muestra dos modos de activación: mediante señal de reset (indeseada, que requiere filtrado) y mediante un trigger válido tras el período de temporización.

.png)

Activación por reset (izquierda) y por trigger válido (derecha)

Lógica de Habilitación de Alarma

Implementada con un opamp como comparador, actúa como compuerta AND analógica para evitar falsos positivos durante el reset del sistema. Solo cuando el trigger está activo (bajo) y el reset está inactivo (alto) se genera la señal de alarma.

.png)

Lógica AND analógica: alarma solo con trigger activo y reset inactivo

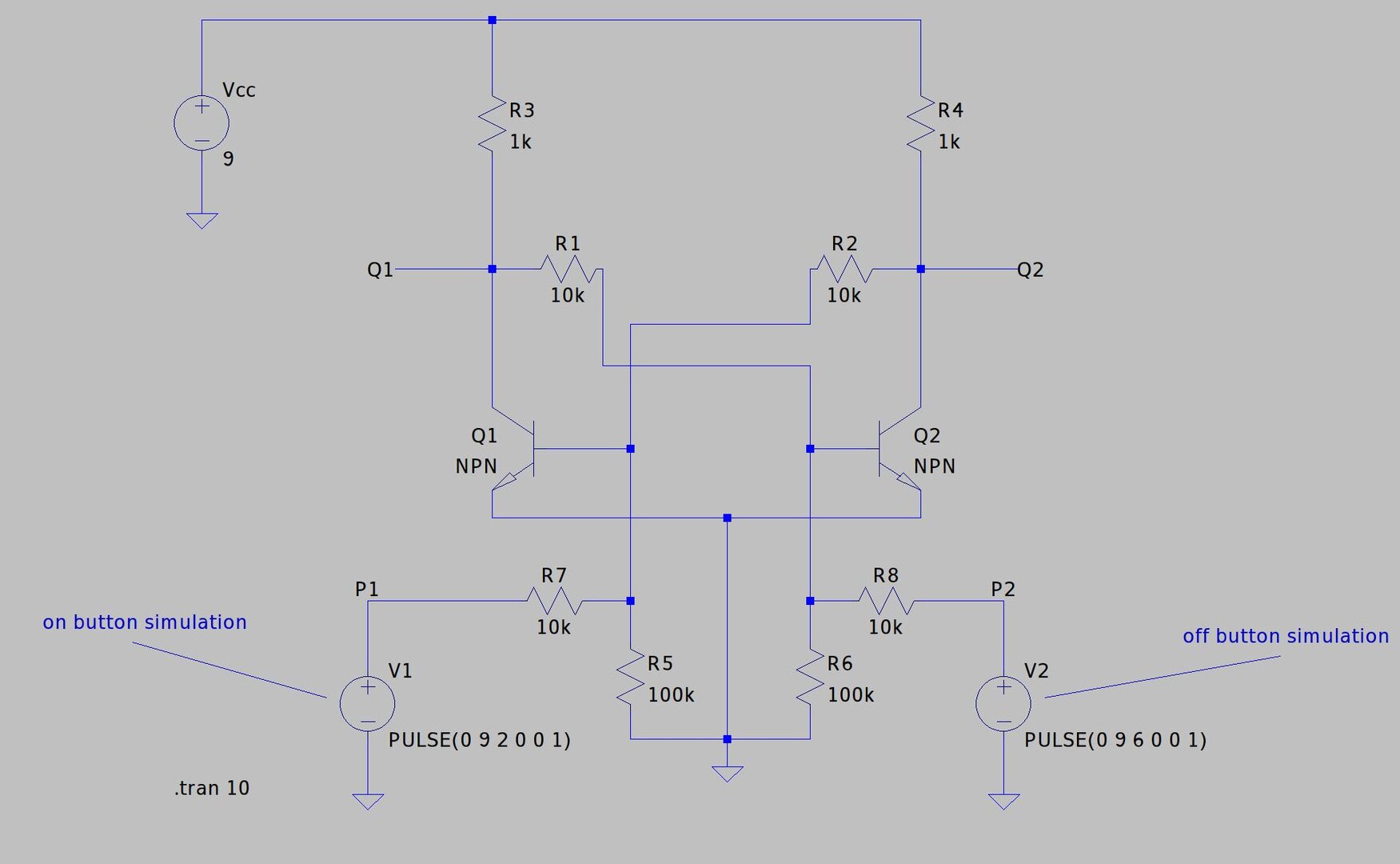

3. Latch Analógico con Transistores NPN

Latch simple implementado con dos transistores NPN cruzados que mantiene un estado estable (ON/OFF) hasta recibir una señal de conmutación opuesta. Se utiliza para retener el estado de despliegue de los paneles solares.

Latch analógico: configuración cruzada de transistores NPN para retención de estado

.png)

Estado 1: Q1 activo, Q2 inactivo - salida estable

.png)

Estado 2: Q2 activo, Q1 inactivo - conmutación limpia

El latch responde correctamente a pulsos de entrada, manteniendo el último estado activado sin consumo adicional hasta la siguiente conmutación. La simulación confirma una transición estable entre estados sin oscilaciones.

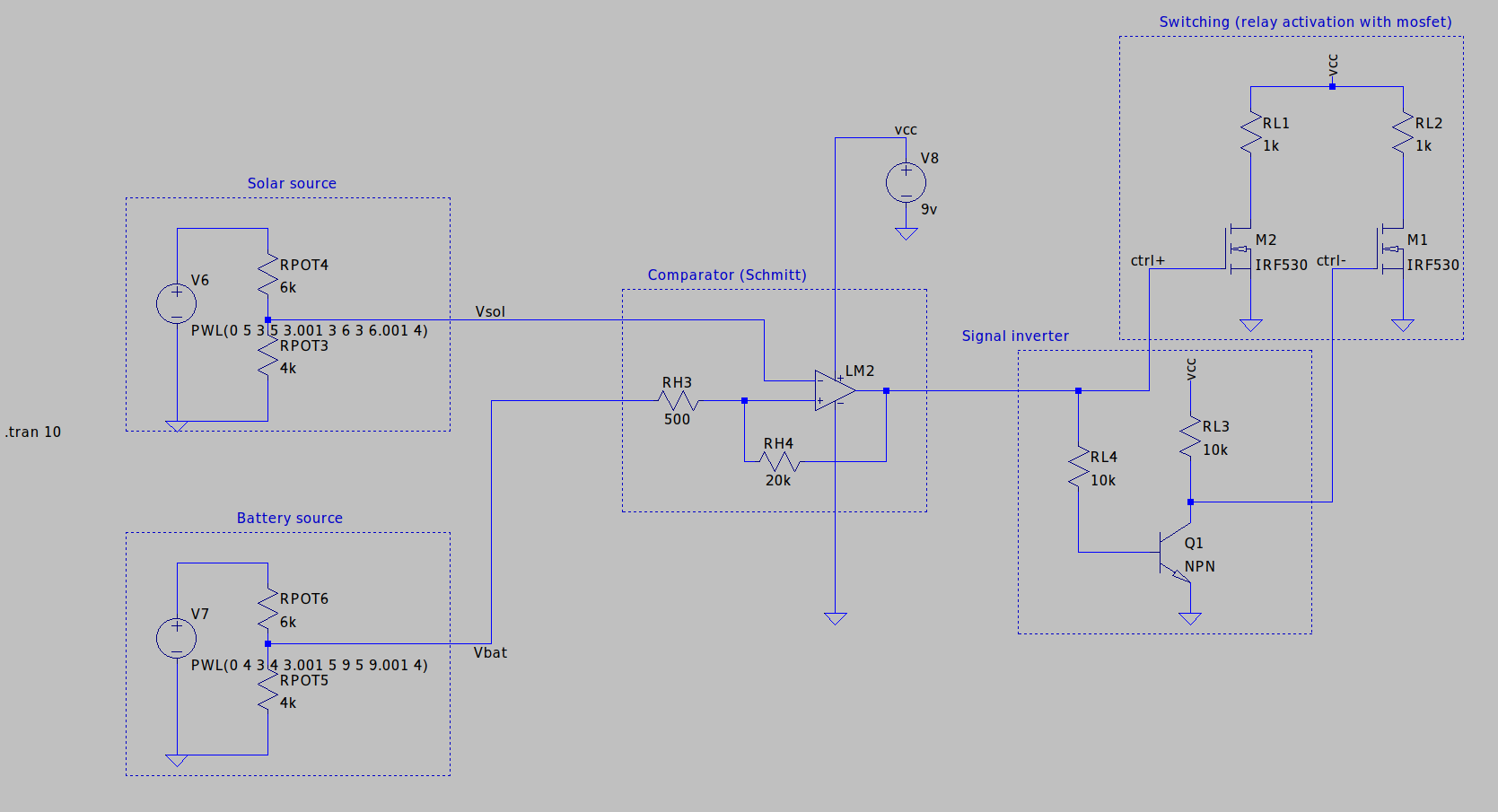

4. Conmutación de Fuentes con MOSFET

Etapa de control para activación de relays mediante MOSFETs, que gestionan la selección entre fuente solar y baterías. La simulación se centra en el comportamiento del MOSFET, ya que el relay opera como carga inductiva controlada.

Driver MOSFET con protección y señal de control desde comparador

.png)

Conmutación limpia: señal de mosfets para relé solar (rojo) y batería (azul) sin retrasos significativos

El MOSFET CSD17577Q5A responde eficientemente a la señal de control, con tiempos de conmutación rápidos y sin oscilaciones. La simulación valida que el diseño maneja correctamente la transición entre fuentes de alimentación.

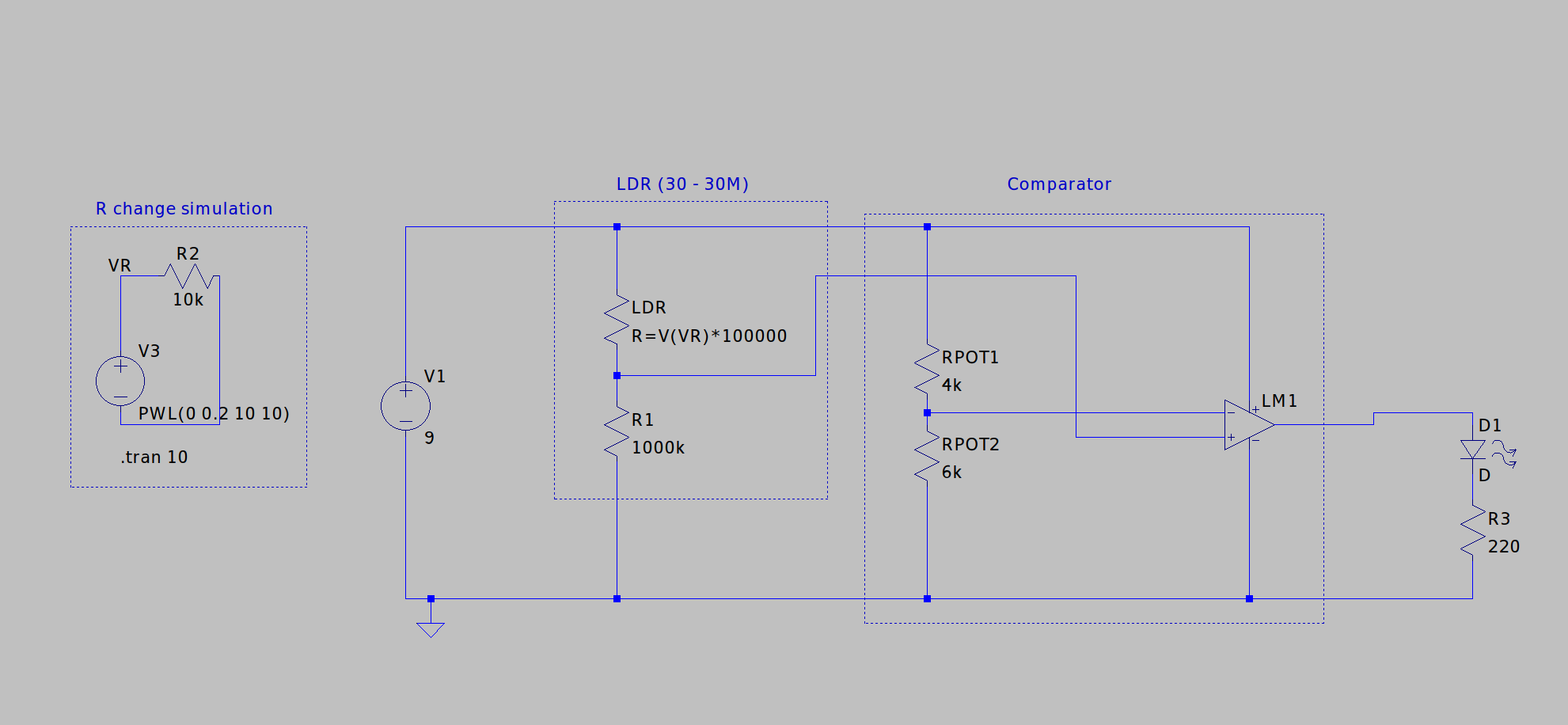

5. Simulación de Sensor de Orientación con LDR

Simulación del circuito de detección de orientación que utiliza un LDR (Light Dependent Resistor) en configuración de divisor resistivo seguido de un comparador. Para modelar la variación de resistencia del LDR en LTSpice, se implementó una solución creativa: una fuente de voltaje PWL variable que controla el valor de una resistencia mediante la expresión R = V(VR) * 100000, simulando efectivamente una resistencia que cambia en el tiempo.

Divisor resistivo con "LDR variable" (fuente PWL controlada) y etapa comparadora

.png)

Respuesta del sistema: voltaje del divisor (variable, azul) y salida del comparador (escalón, rojo)

La simulación confirma que el circuito detecta correctamente cuando la iluminación (simulada como resistencia variable) cruza el umbral establecido, generando una transición limpia en la salida del comparador.